Wir entwickeln in einem kleinen Team Hard- und Software für moderne Sensorik mit anspruchsvoller Realtime-Signalverarbeitung.

Aktuell bieten wir verschiedene Themen als Bachelor-/Master-Arbeit oder Werksstudenten Tätigkeit an:

- Erweiterung und Integration eines bestehenden Radars -Backend:

Der Schwerpunkt liegt hier auf der Integration bestehender High-Speed AD-Wandler Systeme mit einem Radar-Waveform-Generator in einem 2 HE 19 Zoll Rack. Dabei sind u.a. Anpassungen an dem AD-Wandler Verstärkerstufe vorzunehmen, eine Neu- bzw. Weiterentwicklung eines vorhandenen HF-tauglichen DCDC Netzteils, sowie die Planung und Anordnung der Bauteile im Gehäuse und die Gestaltung der Frontplatte zu erarbeiten. Auf das Anfertigen von Mess-Protokollen und Dokumentation wird großen Wert gelegt.

Bachelor-Arbeit/Werkstudenten Tätigkeit, ab sofort

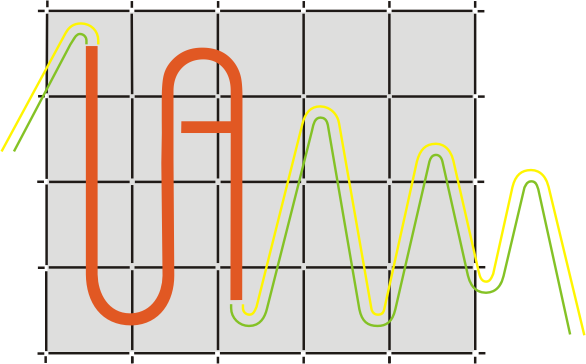

- Entwurf und Implementierung einer DDS im FPGA für nicht lineare Radar-Waveforms:

Mit einer DDS (Direkte Digitale Synthese) können generell periodische Signale mit praktisch beliebiger Frequenzauflösung digital erzeugt werden. Ziel ist es, eine Ansteuerung für eine DDS so zu entwickeln, dass nicht lineare Radar-Waveforms (z.b. hyperbolische, exponentiell oder Code-basisert) erzeugt werden können. Dabei soll zunächst eine Matlab-Simulation zum generellen Verständnis durchgeführt werden, anschließend soll die Funktionalität im FPGA mittels VHDL implementiert werden. Dabei steht bereits ein DDS-Block zur Verfügung, welcher mit den neuen Funktionen erweitert werden kann. Die implementierte DDS wird mittels onChip-Logic-Analysern verifiziert.

Master-Arbeit, ab sofort

- Ausgabe von FPGA verarbeiteten Radar-Daten mittels HDMI (FPGA):

Für ein bestehendes FPGA Projekt sollen Radar-Daten direkt über eine HDMI-Schnittstelle ausgegeben werden. Hierzu soll im FPGA ein HDMI-Interface entwickelt werden, welches die Radar-Daten soweit anpasst, dass diese HDMI gerecht ausgegeben werden können, dazu zählen u.a. die Color-Map und Interpolation der Daten auf eine feste Bildschirmauflösung. Evtl. ist auch ein Overlay von zusätzlichen Informationen vorgesehen. Für das HDMI-Interface kann bereits auf fertige Lösungen zurückgegriffen werden, welche dann als Ausgangspunkt für die weitere Implementierung im FPGA dienen. Die Implementierung soll in VHDL erfolgen und kann mittels onChip-Logic-Analysern verifiziert werden.

Master-Arbeit, ab sofort

- Entwicklung eines Linux Kernel Moduls für extrem schnelle ETH-Kommunikation:

Es soll ein Kernel-Modul für Linux entwickelt werden, welches die Daten direkt bei der Netzwerkkarte abgreift und gemäß einem eigenen Protokoll verarbeitet und in einem konfigurierbaren Buffer (FIFO) zwischenspeichert. Ziel ist es, keinen Interrupt für jedes ankommende Paket an den User-Space weiter zu reichen sondern nur dann wenn der Buffer voll ist. Im User-Space sollen dann C++ Programme oder auch Matlab auf die Daten im Buffer zugreifen können (wünschenswert alles copyless), d.h. es ist eine API zu entwickeln. Zunächst soll dieses für 2 ETH-Kanäle realisiert werden, in der letzten Ausbaustufe sind dann 8 ETH-Kanäle möglich. Verwendet werden nur Intel-Server Netzwerkkarten.

Master-Arbeit, ab sofort. Dieses Thema richtet sich explizit an Studierende der Fachrichtung Informatik.